# Motorola SEMICONDUCTOR

3501 Ed Bluestein Blvd Austin TX 78721

#### **BIT RATE GENERATOR**

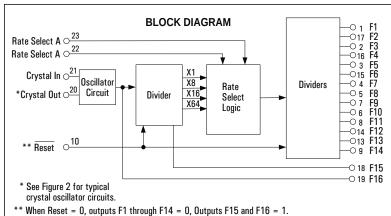

The MC14411 bit rate generator is constructed with complementary MOS enhancement mode devices. It utilizes a frequency divider network to provide a wide range of output frequencies.

A crystal controlled oscillator is the clock source for the network. A two-bit address is provided to select one of four multiple output clock rates.

Applications include a selectable frequency source for the equipment in the data communications market, such as teleprinters, printers, CRT terminals and microprocessor systems.

- Single 5.0Vdc ( ± 5%) Power Supply

- Internal Oscillator Crystal Controlled for Stability (1.8432 Mhz)

- Sixteen Different Output Clock Rates

- 50% Duty Cycle

- Programmable Time Bases for One of Four Multiple Output Rates

- Buffered Outputs Compatible with Low Power TTL

- Noise Immunity = 45% of Vdd Typical

- Diode Protection on All Inputs

- External Clock may be applied to Pin 21

- Internal Pull-up Resistor on Reset Input

#### MAXIMUM RATINGS (Voltages referenced to Vss, Pin 12.)

| Rating                      | Symbol | Value                     | Unit |

|-----------------------------|--------|---------------------------|------|

| DC Supply Voltage Range     | Vdd    | 5.25 to - 0.5             | V    |

| Input Voltage, All Inputs   | Vin    | Vdd + 0.5 to<br>Vss - 0.5 | V    |

| DC Current Drain Per Pin    | I      | 10                        | mA   |

| Operating Temperature Range | Ta     | -40 to +85                | °C   |

| Storage Temperature Range   | Tstg   | -65 to +150               | °C   |

#### men neset - 0, outputs 11 tillough 114 - 0, outputs 113 and 110 - 1.

MC14411

### **CMOS LSI**

(LOW-POWER COMPLEMENTARY MOS)

#### **BIT RATE GENERATOR**

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that Vin and Vout be constrained to the range Vss ≤ (Vin or Vout) ≤ Vdd.

Tie unused inputs to appropriate logic levels

#### **ELECTRICAL CHARACTERISTICS**

| Characteristics                                     | Symbol            | $v_{DD}$        | -40   | 10 °C 25 °C |                                                          | -40 °C 25 °C 85 °C |       | °C    | Unit |         |

|-----------------------------------------------------|-------------------|-----------------|-------|-------------|----------------------------------------------------------|--------------------|-------|-------|------|---------|

|                                                     |                   | V <sub>DC</sub> | Min   | Max         | Min                                                      | Тур                | Max   | Min   | Max  |         |

| Supply Voltage                                      | v <sub>DD</sub>   |                 | 4.75  | 5.25        | 4.75                                                     | 5.0                | 5.25  | 4.75  | 5.25 | V       |

| Output Voltage "O" Level                            | V <sub>out</sub>  | 5.0             |       | 0.05        |                                                          | 0                  | 0.05  |       | 0.05 | V       |

| "1" Level                                           |                   | 5.0             | 4.95  |             | 4.95                                                     | 5.0                |       | 4.95  |      | V       |

| Input Voltage                                       |                   |                 |       |             |                                                          |                    |       |       |      |         |

| $(V_0 = 4.5V \text{ or } 5.0V)$                     |                   | 5.0             |       | 1.5         |                                                          | 2.25               | 1.5   |       | 1.5  | V       |

| $(V_0 = 0.5V \text{ or } 4.5V)$                     | V <sub>IH</sub>   | 5.0             | 3.5   |             | 3.5                                                      | 2.75               |       | 3.5   |      | V       |

| Output Drive Current                                | _                 |                 |       |             |                                                          |                    |       |       |      |         |

| $(V_{OH} = 2.5V)$ Source                            |                   | 5.0             | -0.23 |             | -0.20                                                    | -1.7               |       | -0.16 |      | mA      |

| (V <sub>OL</sub> = 0.4V) Sink                       | IOL               | 5.0             | 0.23  |             | 0.20                                                     | 0.78               |       | 0.16  |      | mA      |

| Input Current                                       | _                 |                 |       |             |                                                          | ±0.00001           |       |       |      | _       |

| Pins 21,22,23                                       | l <sub>in</sub>   | <br>5.0         |       | ± 0.1       | <br>-1.5                                                 | ± 0.00001          | ± 0.1 |       | ±0.1 | $\mu$ A |

| Pin 10                                              |                   | 5.0             |       |             | -1.5                                                     |                    | -7.5  |       |      | μΑ      |

| Input Capacitance                                   | C <sub>in</sub>   |                 |       |             |                                                          | 5.0                |       |       |      | pF      |

| Quiescent Dissipation                               | PQ                | 5.0             |       | 2.5         |                                                          | 0.015              | 2.5   |       | 15   | mW      |

| Power Dissipation **†                               | PD                | 5.0             |       |             |                                                          |                    |       |       |      |         |

| (Dynamic plus Quiescent)<br>(C <sub>I</sub> = 15pF) |                   |                 |       |             | $P_{D} = (7.5 \text{mW/MHZ}) f + P_{Q} \qquad \text{mW}$ |                    | mW    |       |      |         |

| Output Rise Time **                                 | <sup>t</sup> TLH  | 5.0             |       | -           | -                                                        | 70                 | 200   |       |      | ns      |

| $T_f = (3.0 \text{ ns/pF}) C_L + 25 \text{ns}$      |                   |                 |       |             |                                                          |                    |       |       |      |         |

| Output Fall Time **                                 | <sup>t</sup> THL  | 5.0             |       |             |                                                          | 70                 | 200   |       |      | ns      |

| $T_f = (1.5 \text{ ns/pF}) C_L + 47 \text{ns}$      |                   |                 |       |             |                                                          |                    |       |       |      |         |

| Input Clock Frequency                               | fCL               | 5.0             |       | 1.85        |                                                          |                    | 1.85  |       | 1.85 | MHz     |

| Clock Pulse Width                                   | <sup>t</sup> W(C) |                 | 200   | -           | 200                                                      | -                  |       | 200   |      | ns      |

| Reset Pulse Width                                   | <sup>t</sup> W(r) |                 | 500   | -           | 500                                                      | -                  | -     | 500   | -    | nz      |

<sup>†</sup> For dissipation at different external capacitance (C<sub>L</sub>) refer to the corresponding formula:  $P_T = (C_L = P_D + 2.6 \text{ x} 10^{-3} \text{ (C}_{L} - 15 \text{pF) V}_{DD} \text{ } 2^f$

Where:  $\text{P}_{T}, \text{P}_{D}$  in mW,  $\text{C}_{L}$  in pF,  $\text{V}_{DD}$  in  $\text{V}_{dc}$  and f in MHz

\*\* The formula given is for typical characteristics only.

Table 1 – Output Clock Rates

| Rate |   |      |

|------|---|------|

| В    | Α | Rate |

| 0    | 0 | X1   |

| 0    | 1 | Х8   |

| 1    | 0 | X16  |

| 1    | 1 | C64  |

| Output |        | Output Rates (Hz) |        |        |  |  |  |

|--------|--------|-------------------|--------|--------|--|--|--|

| Number | X64    | X16               | X8     | X1     |  |  |  |

| F1     | 614.4K | 153.6K            | 76.8K  | 9600   |  |  |  |

| F2     | 460.8K | 115.2K            | 57.6K  | 7200   |  |  |  |

| F3     | 307.2K | 76.8K             | 38.4K  | 4800   |  |  |  |

| F4     | 230.4K | 57.6K             | 28.8   | 3600   |  |  |  |

| F5     | 153.6K | 38.4K             | 19.2K  | 2400   |  |  |  |

| F6     | 115.2K | 28.8              | 14.4k  | 1800   |  |  |  |

| F7     | 76.8K  | 19.2K             | 9600   | 1200   |  |  |  |

| F8     | 38.4K  | 9600              | 4800   | 600    |  |  |  |

| F9     | 19.2K  | 4800              | 2400   | 300    |  |  |  |

| F10    | 12.8K  | 3200              | 1600   | 200    |  |  |  |

| F11    | 9600   | 2400              | 1200   | 150    |  |  |  |

| F12    | 8613.2 | 2153.3            | 1076.6 | 134.5  |  |  |  |

| F13    | 7035.5 | 1758.8            | 879.4  | 109.9  |  |  |  |

| F14    | 4800   | 1200              | 600    | 75     |  |  |  |

| F15    | 921.6K | 921.6k            | 921.6k | 921.6k |  |  |  |

| F16*   | 1.843M | 1.834M            | 1.834M | 1.834M |  |  |  |

## MOTOROLA SEMICONDUCTOR

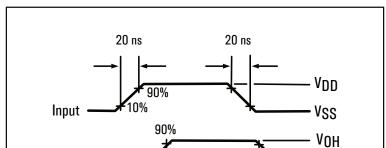

FIGURE 1 - DYNAMIC SIGNAL WAVEFORMS

Output

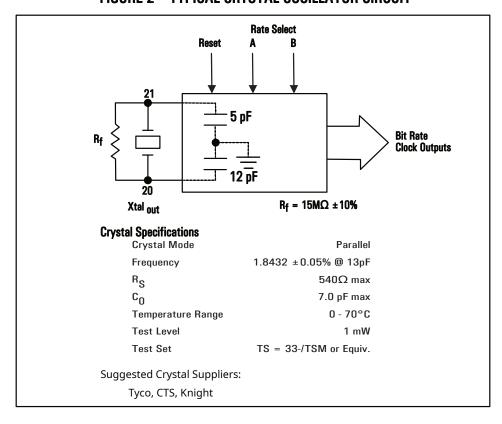

FIGURE 2 - TYPICAL CRYSTAL OSCILLATOR CIRCUIT

VOL

## MOTOROLA SEMICONDUCTOR

With X1 Rate setting (A&B LOW) Rates are shown.

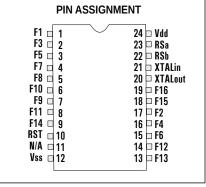

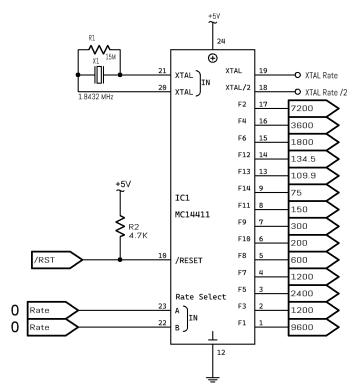

This integrated circuit simultaneously generates 16 reference frequencies useful with serial interface clock speeds. In normal operation, pin 24 tied to  $\pm 5V$ , pin 12 is tied to ground and pin 10 is tied to  $\pm 5V$  through a pull-up resistor, allowing pin 10 to be pulled low for reset.

Pins 22 and 23 are used to program the the output frequencies based on the primary crystal frequency by providing various frequency divisions of 1X, 8X, 16X and 64X. The Baud Rate output frequencies are supplied on pins 1 through 9 and and 13 through 17. Each of these outputs can drive one TTL load or multiple CMOS loads.

The nominal frequency for the attached crystal is 1.8432 MHZ and is attached to pins 20 and 21 along with a bias resistor. The crystal frequency is output on pin 19 and this frequency divided by 2 is output on pin 18 and operate independently of the other frequency outputs. These outputs could be used to supply system clock, for example.

All outputs are symmetrical with 50% duty cycle.

## **Application Information**

Typical applications of the Bit Rate Generator (BRG) include providing standard clock frequencies for data communications equipment, and external synchronization of a BRG output to a data source. The synchronization is accomplished by releasing the Reset input of the BRG during a data transition of the data source.

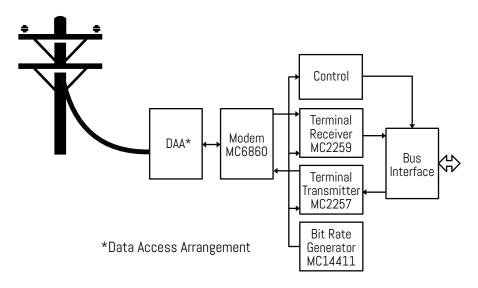

A typical data communication system is shown in Figure 3. In this example a standard frequency from the BRG is used for the clock input to the terminal transmitter and receiver (MC2257, MC2259). In a similar system the BRG, via Rate Select inputs, can provide up to 64 standard data communications frequencies, for a multiple frequency system. Some examples of equipment frequency requirements are shown in Table 2.

## TYPICAL DATA COMMUNICATION TERMINAL BLOCK DIAGRAM

Table 2– Typical Data Communications Equipment Bit Rate Frequencies

| Frequency (HZ)                           | Use                                                                                                     |

|------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 75<br>110<br>134.49<br>150<br>200<br>300 | Asynchronous Mode<br>Teleprinters<br>Printers, typewriters<br>CRT Terminals<br>etc                      |

| 600<br>1200                              | Asynchronous Mode (High<br>Speed)<br>Printers, typewriters<br>Credit Card Verification<br>CRT Terminals |

| 2400<br>3600<br>4800<br>7200<br>9600     | Synchronous Mode<br>Computer to Computer<br>Or<br>Computer to Peripheral                                |